Design a Computer

目录

Design a Computer

github: https://github.com/naughtz/design-a-computer

本项目使用vivado2018.2进行开发,使用的开发板为EGO1。实现了16条MIPS指令,并用这些指令实现二叉树中序遍历的功能。CPU的设计、测试与voldemortX及小组成员们共同完成。

实现内容

指令集

| 指令 | op | 格式 | |||||

| add | 000000 | rs | rt | rd(rs+rt) | 00000 | 100000 | |

| or | 000000 | rs | rt | rd(rs|rt) | 00000 | 100101 | |

| sub | 000000 | rs | rt | rd(rs-rt) | 00000 | 100010 | |

| xor | 000000 | rs | rt | rd(rs^rt) | 00000 | 100110 | |

| addi | 001000 | rs | rt | imm16 | |||

| andi | 001100 | rs | rt | imm16 | |||

| xori | 001110 | rs | rt | imm16 | |||

| bne | 000101 | rs | rt | offset16 | |||

| beq | 000100 | rs | rt | offset16 | |||

| sw | 101011 | rs | rt | offset16 | |||

| lw | 100011 | rs | rt | offset16 | |||

| j | 000010 | target26 | |||||

| jal | 000011 | target26 | |||||

| jr | 000000 | rs | 000000000000000(15) | 001000 | |||

| sll | 000000 | 00000 | rt | rd | shamt5 | 000000 | |

| srl | 000000 | 00000 | rt | rd | shamt5 | 000010 | |

功能

- 输入:

- 内存中事先保存好一棵二叉树,每个节点至少包括3个域:指向左子树的指针、指向右子树的指针、一个ASCII码值表示的字母(互不相同)

- 按中“中”键开始运行程序

- 处理:

- 对该二叉树进行中序遍历

- 输出:

- 处理完毕,数码管显示"in"

- 从结果序列的第1项开始,每按一次“右”键,数码管依次向后显示下一个结点的字母,按“左”键可回看之前的各项

设计

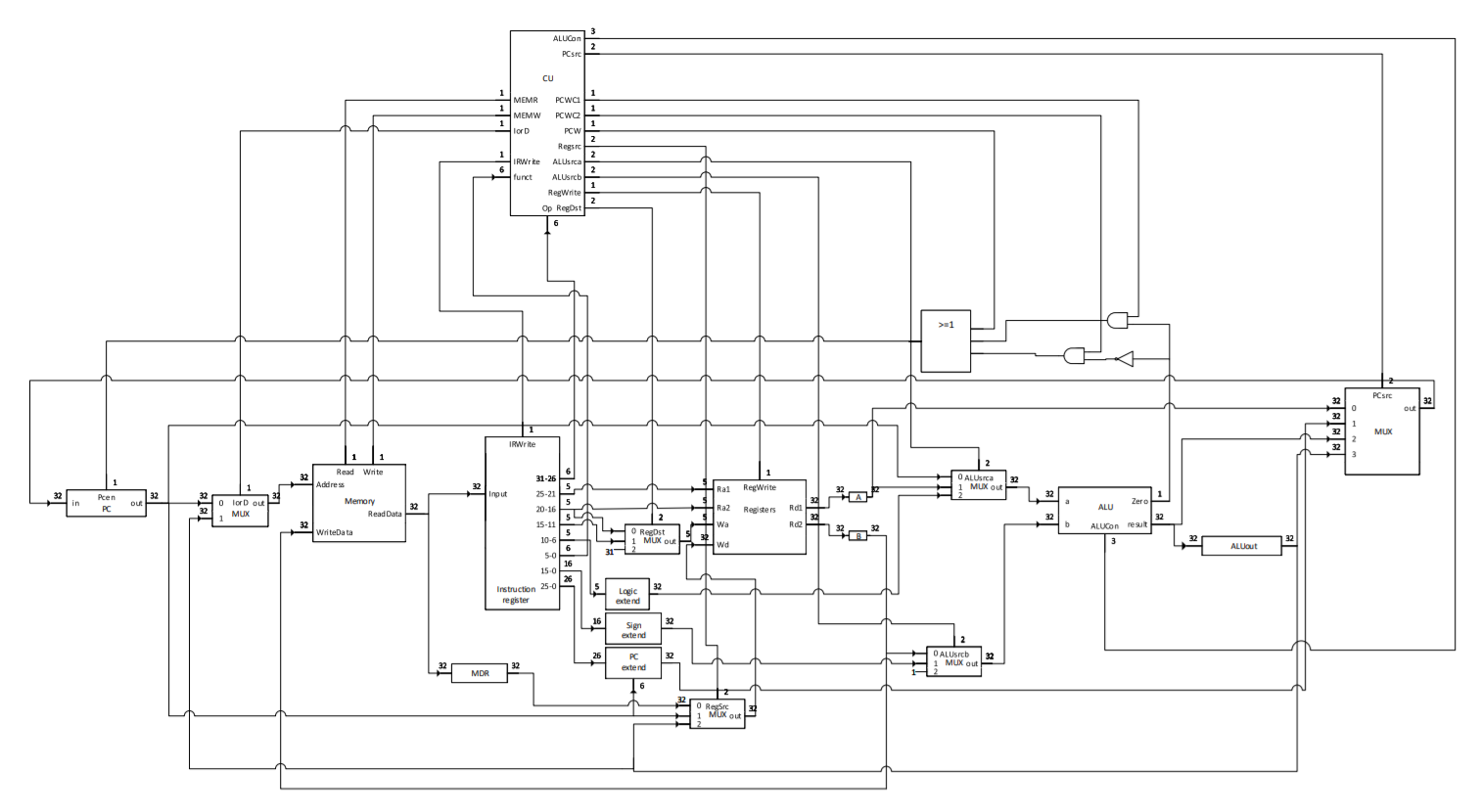

数据通路图

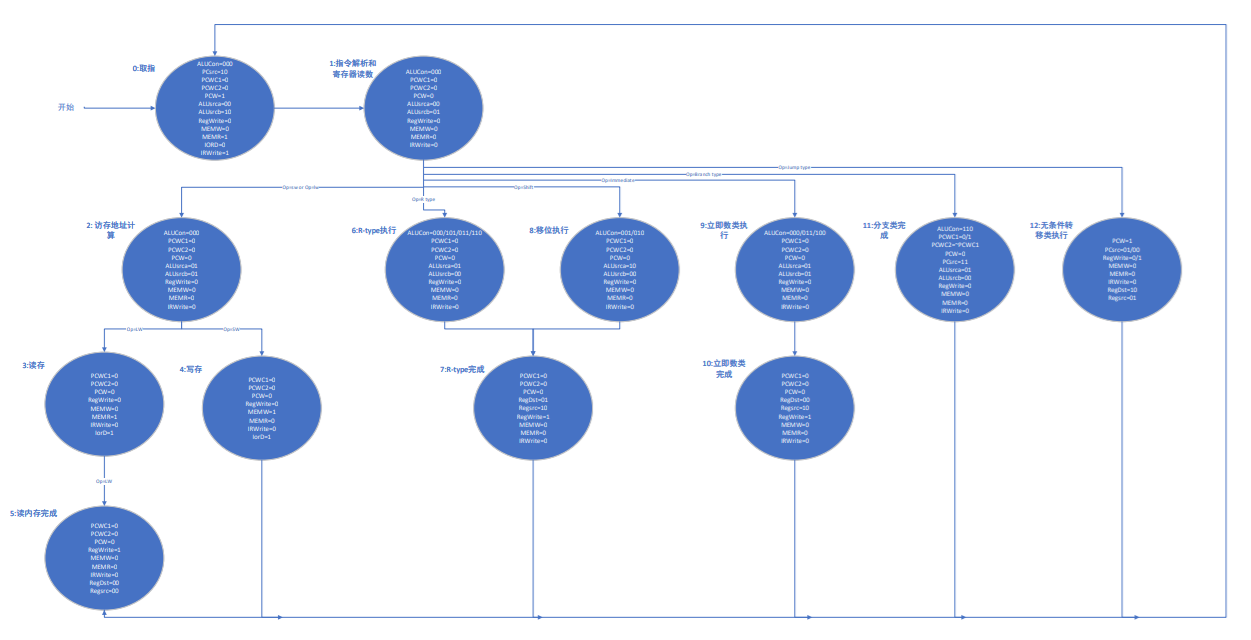

状态转换图

编址

- I/O与主存统一编址

- 使用一块1024*32ROM作为指令存储器,一块1024*32RAM作为数据存储器

- ROM首地址为0H,RAM首地址为400H

- led灯地址为3FF0H,按键地址为3FF1H,数码管地址为3FF2H

- 为了方便,采用32位地址线

指令执行

- add: 指令进入指令寄存器,31-26位op及5-0位funct送至控制器,25-21位、20-16位分别送至寄存器读地址Ra1、Ra2,读出数据至A、B寄存器,再进入运算器的a、b操作数,得出结果送回寄存器写数据Wd,此时寄存器写地址为指令15-11位,至此rs+rt=>rd指令完成。

- addi: 指令进入指令寄存器,31-26位op及5-0位funct送至控制器,25-21位送至寄存器读地址Ra1,读出数据至A寄存器,再进入运算器的a操作数,15-0位立即数符号扩展后进入运算器的b操作数,得出结果送回寄存器写数据wd,此时寄存器写地址为指令20-16位,至此rs+imm16=>rt指令完成。

- bne: 指令进入指令寄存器,PC的值进入运算器的a操作数,指令15-0位offset进入运算器的b操作数,求和后存入ALUout,作为若需修改PC时的PC来源;31-26位op及5-0位funct送至控制器,25-21位、20-16位分别送至寄存器读地址Ra1、Ra2,读出数据至A、B寄存器,再进入运算器的a、b操作数,将零标志位取反后与PCWC2相与,控制PC是否修改。

- 其它指令类似,根据图可容易地理出执行流程。

汇编算法

- 二叉树的每个结点由3个字组成,第一个字为左子树地址,第二个字为该结点表示字母的ASCII码,第三个字为右子树地址

- 使用递归算法,需在内存开一个栈用于保存每次递归返回的地址及参数

- 出栈顺序即为中序遍历顺序,将其保存在连续的一段内存中,方便查看结果

- 具体代码见"汇编"文件夹

注意

按键

- EGO1开发板的reset键默认为高电平,按下为低电平;五个通用按键默认为低电平,按下为高电平。

访存时间

- 我们采用了ROM与RAM的IP核,测试时发现访存时间不稳定,于是将CPU频率降至主存频率的一半,以解决此问题。

指令

- 本项目只实现了16条指令,如果使用一些软件进行汇编-机器的翻译,某些特殊情况会出现翻译出不在这16条指令中的指令(如:翻译软件检测到它认为不能实现的操作,翻译时自动寻找替代的指令)

参考文献

- [1]David,A.Patterson&John,L.Hennessy: Computer Organization And Design 3th[M]. San Francisco: Margan Kaufmann, 2005